# Horizon 2020

# **Call: H2020-FETHPC-2016-2017** (FET Proactive – High Performance Computing)

# Topic: FETHPC-02-2017

## **Type of action: RIA** (Research and Innovation action)

# Proposal number: 800929

# **Proposal acronym: DIO**

## Deadline Id: H2020-FETHPC-2017 Table of contents

| Section | Title                   | Action |

|---------|-------------------------|--------|

| 1       | General information     |        |

| 2       | Participants & contacts |        |

| 3       | Budget                  |        |

| 4       | Ethics                  |        |

| 5       | Call-specific questions |        |

## How to fill in the forms

The administrative forms must be filled in for each proposal using the templates available in the submission system. Some data fields in the administrative forms are pre-filled based on the previous steps in the submission wizard.

Page 1 of 30

| Proposal ID | 800929 |

|-------------|--------|

|-------------|--------|

Acronym DIO

## 1 - General information

| Торіс              | FETHPC-02-2017                                                                                                        |         |

|--------------------|-----------------------------------------------------------------------------------------------------------------------|---------|

| Call Identifier    | H2020-FETHPC-2016-2017                                                                                                |         |

| Type of Action     | RIA                                                                                                                   |         |

| Deadline Id        | H2020-FETHPC-2017                                                                                                     |         |

| Acronym D          | 010                                                                                                                   |         |

| Proposal title*    | High Density I/O Path for Fast Storage Devices and Multi-tier Hierarchies                                             |         |

|                    | Note that for technical reasons, the following characters are not accepted in the Proposal Title and will be removed: | < > " & |

| Duration in months | 36                                                                                                                    |         |

| Fixed keyword 1    | High performance computing Add                                                                                        |         |

| Fixed keyword 2    | Computer systems, parallel/distributed systems, sensor network Add Remove                                             |         |

| Fixed keyword 3    | System Software Add Remove                                                                                            |         |

| Fixed keyword 4    | Scalability Add Remove                                                                                                |         |

| Free keywords      | Enter any words you think give extra detail of the scope of your proposal (max 200 character with spaces).            | rs      |

Proposal ID 800929

Acronym DIO

#### Abstract

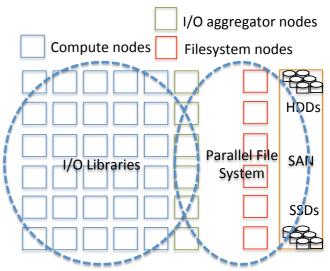

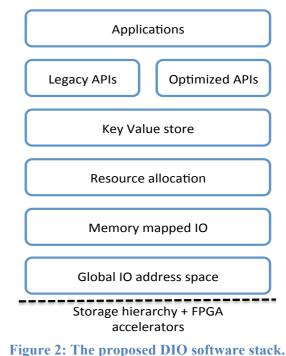

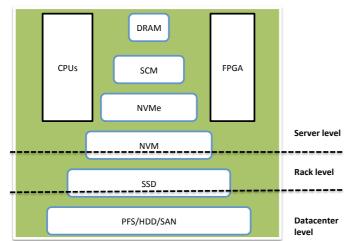

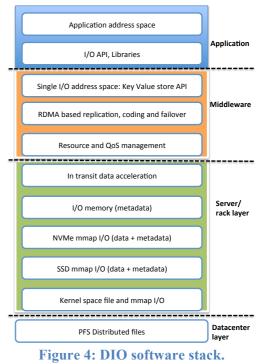

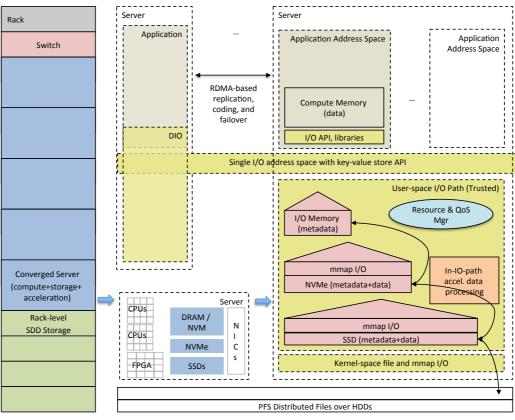

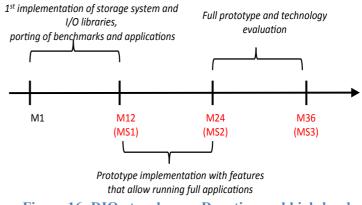

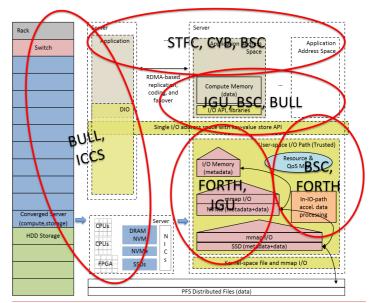

DIO will design, prototype, and demonstrate an I/O software stack for deep storage hierarchies that incorporates the following technology innovations and methodology:

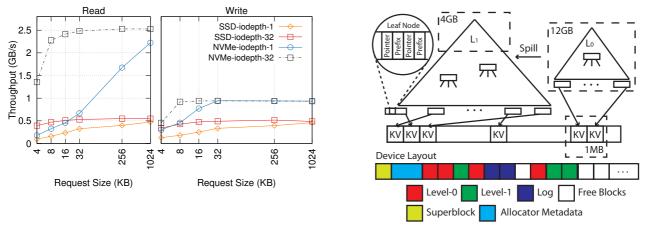

(a) Global I/O address space via partitioning, placing, and indexing data on devices, based on multi-level write-optimized data structures that have emerged in the area of analytics and have the ability to inherently adapt to different device technologies at each level/tier.

(b) Novel memory-mapped I/O approach for fast devices, such as NVMe and NVM, to organize and access data directly on devices, which will eliminate all software path overhead in the common I/O path, both for caching (hits) and data access (kernel crossings). DIO will use transparent data replication at the mmap level to replicate data over fast remote devices using RDMA and failure atomicity based on copy-on-write.

(c) Use of FPGA acceleration for near-device processing both for reducing I/O overheads, such as replication coding, but also for offloading application-induced data transformations that can be performed during data replacement.

(d) Support legacy APIs for existing applications but will also explore new capabilities, especially with relation to device (tier) technology and in-I/O-path acceleration.

(e) Use of a key-value based abstraction for locating and accessing data, which will allow sharing, access, and prioritization at fine grain and on a per-pair basis.

(f) Mechanisms and policies for allocating resources to concurrent applications and diverse workloads that exhibit highdegrees of parallelism and require dynamic data placement across tiers to achieve both deterministic application QoS and high system utilization.

(g) Converged rack-scale architecture for bringing the proposed technology to next-generation systems.

202

Remaining characters

Has this proposal (or a very similar one) been submitted in the past 2 years in response to a call for proposals under Horizon 2020 or any other EU programme(s)?

Proposal ID 800929

Acronym DIO

#### Declarations

| 1) The coordinator declares to have the explicit consent of all applicants on their participation and on the content of this proposal.                                                                                                                                                                     | $\boxtimes$ |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 2) The information contained in this proposal is correct and complete.                                                                                                                                                                                                                                     | $\boxtimes$ |

| 3) This proposal complies with ethical principles (including the highest standards of research integrity — as set out, for instance, in the European Code of Conduct for Research Integrity — and including, in particular, avoiding fabrication, falsification, plagiarism or other research misconduct). | $\boxtimes$ |

#### 4) The coordinator confirms:

|   | - to have carried out the self-check of the financial capacity of the organisation on <a href="http://ec.europa.eu/research/participants/portal/desktop/en/organisations/lfv.html">http://ec.europa.eu/research/participants/portal/desktop/en/organisations/lfv.html</a> or to be covered by a financial viability check in an EU project for the last closed financial year. Where the result was "weak" or "insufficient", the coordinator confirms being aware of the measures that may be imposed in accordance with the H2020 Grants Manual (Chapter on Financial capacity check); or | О |  |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--|

|   | - is exempt from the financial capacity check being a public body including international organisations, higher or secondary education establishment or a legal entity, whose viability is guaranteed by a Member State or associated country, as defined in the H2020 Grants Manual (Chapter on Financial capacity check); or                                                                                                                                                                                                                                                              | ۲ |  |

| Ĩ | - as sole participant in the proposal is exempt from the financial capacity check.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0 |  |

5) The coordinator hereby declares that each applicant has confirmed:

| - they are fully eligible in accordance with the criteria set out in the specific call for proposals; and                         | $\boxtimes$ |  |

|-----------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| - they have the financial and operational capacity to carry out the proposed action.                                              | $\square$   |  |

| The coordinator is only responsible for the correctness of the information relating to his/her own organisation. Each application |             |  |

The coordinator is only responsible for the correctness of the information relating to his/her own organisation. Each applicant remains responsible for the correctness of the information related to him/her and declared above. Where the proposal to be retained for EU funding, the coordinator and each beneficiary applicant will be required to present a formal declaration in this respect.

According to Article 131 of the Financial Regulation of 25 October 2012 on the financial rules applicable to the general budget of the Union (Official Journal L 298 of 26.10.2012, p. 1) and Article 145 of its Rules of Application (Official Journal L 362, 31.12.2012, p.1) applicants found guilty of misrepresentation may be subject to administrative and financial penalties under certain conditions.

#### Personal data protection

The assessment of your grant application will involve the collection and processing of personal data (such as your name, address and CV), which will be performed pursuant to Regulation (EC) No 45/2001 on the protection of individuals with regard to the processing of personal data by the Community institutions and bodies and on the free movement of such data. Unless indicated otherwise, your replies to the questions in this form and any personal data requested are required to assess your grant application in accordance with the specifications of the call for proposals and will be processed solely for that purpose. Details concerning the purposes and means of the processing of your personal data as well as information on how to exercise your rights are available in the <u>privacy statement</u>. Applicants may lodge a complaint about the processing of their personal data with the European Data Protection Supervisor at any time.

Your personal data may be registered in the Early Detection and Exclusion system of the European Commission (EDES), the new system established by the Commission to reinforce the protection of the Union's financial interests and to ensure sound financial management, in accordance with the provisions of articles 105a and 108 of the revised EU Financial Regulation (FR) (Regulation (EU, EURATOM) 2015/1929 of the European Parliament and of the Council of 28 October 2015 amending Regulation (EU, EURATOM) No 966/2012) and articles 143 - 144 of the corresponding Rules of Application (RAP) (COMMISSION DELEGATED REGULATION (EU) 2015/2462 of 30 October 2015 amending Delegated Regulation (EU) No 1268/2012) for more information see the Privacy statement for the EDES Database).

Page 4 of 30

Proposal ID 800929

Acronym DIO

## List of participants

| # | Participant Legal Name                                                | Country        |

|---|-----------------------------------------------------------------------|----------------|

| 1 | FOUNDATION FOR RESEARCH AND TECHNOLOGY HELLAS                         | Greece         |

| 2 | BARCELONA SUPERCOMPUTING CENTER - CENTRO NACIONAL DE SUPERCOMPUTACION | Spain          |

| 3 | SCIENCE AND TECHNOLOGY FACILITIES COUNCIL                             | United Kingdom |

| 4 | BULL SAS                                                              | France         |

| 5 | JOHANNES GUTENBERG-UNIVERSITAT MAINZ                                  | Germany        |

| 6 | INSTITUTE OF COMMUNICATION AND COMPUTER SYSTEMS                       | Greece         |

| 7 | CYBELETECH SAS                                                        | France         |

Page 5 of 30

Proposal ID 800929

Acronym DIO

Short name FORTH

Legal person ..... yes

## 2 - Administrative data of participating organisations

| PIC             | Legal name                                    |

|-----------------|-----------------------------------------------|

| 999995893       | FOUNDATION FOR RESEARCH AND TECHNOLOGY HELLAS |

| Chart name: EOD | TII                                           |

Short name: FORTH

#### Address of the organisation

Street N PLASTIRA STR 100

- Town HERAKLION

- Postcode 70013

- Country Greece

- Webpage www.forth.gr

#### Legal Status of your organisation

#### **Research and Innovation legal statuses**

| Public bodyno                                     |

|---------------------------------------------------|

| Non-profityes                                     |

| International organisationno                      |

| International organisation of European interestno |

| Secondary or Higher education establishmentno     |

| Research organisationyes                          |

|                                                   |

#### **Enterprise Data**

SME self-declared status

11/05/2016 - no

SME self-assessment

unknown

SME validation sme

25/09/2008 - no

Based on the above details of the Beneficiary Registry the organisation is not an SME (small- and medium-sized enterprise) for the call.

H2020-CP-2016-v2.pdf Ver1.00 20170223

Page 6 of 30

| Character of dependence                       | Participant |  |  |  |  |

|-----------------------------------------------|-------------|--|--|--|--|

| Dependencies with other proposal participants |             |  |  |  |  |

Country

Greece

| European Commission<br>Research & Innovation - Participant Portal<br>Proposal Submission Forms |                                                                         |              |              |              |                          |                                                       |

|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|--------------|--------------|--------------|--------------------------|-------------------------------------------------------|

| European<br>Commission                                                                         |                                                                         |              |              |              |                          |                                                       |

| Prop                                                                                           | oosal ID 800929                                                         | Acronym      | DIO          | Short name   | FORTH                    |                                                       |

| Person in cha                                                                                  | rge of the proposal                                                     |              |              |              |                          |                                                       |

|                                                                                                | ail of contact persons are read-on<br>ntact details of contact persons, |              |              |              |                          | n be edited here. To give access<br>save the changes. |

| Title                                                                                          | Prof.                                                                   |              |              | Sex          | <ul> <li>Male</li> </ul> | ○ Female                                              |

| First name                                                                                     | Angelos                                                                 |              |              | Last name    | BILAS                    |                                                       |

| E-Mail                                                                                         | bilas@ics.forth.gr                                                      |              |              |              |                          |                                                       |

| Position in org.                                                                               | Associated Faculty Member                                               | r            |              |              |                          |                                                       |

| Department                                                                                     | Institute of Computer Science                                           | ce / CARV La | aboratory    |              |                          | Same as organisation                                  |

|                                                                                                | Same as organisation address                                            |              |              |              |                          |                                                       |

| Street                                                                                         | N PLASTIRA STR 100                                                      |              |              |              |                          | ]                                                     |

| Town                                                                                           | HERAKLION                                                               |              |              | Post code 70 | 0013                     |                                                       |

| Country                                                                                        | Greece                                                                  |              |              |              |                          |                                                       |

| Website                                                                                        | http://www.ics.forth.gr/~bilas                                          | S            |              |              |                          |                                                       |

| Phone 1                                                                                        | -30 2810391669                                                          | Phone 2      | FXXX XXXXXXX | κχ           | Fax                      | +30 2810391661                                        |

## Other contact persons

| First Name | Last Name E-mail |                        | Phone |

|------------|------------------|------------------------|-------|

| Christos   | Kozanitis        | kozanitis@ics.forth.gr |       |

| Manolis    | Marazakis        | maraz@ics.forth.gr     |       |

| Ioannis    | Stratakis        | gstra@ics.forth.gr     |       |

Page 8 of 30

This proposal version was submitted by Angelos BILAS on 26/09/2017 07:43:10 Brussels Local Time. Issued by the Participant Portal Submission Service.

| Propo                                       | sal ID 800929         | Acronym     | DIO      | Short name BSC                        |

|---------------------------------------------|-----------------------|-------------|----------|---------------------------------------|

| PIC Legal name<br>999655520 BARCELONA SUPER |                       | PERCOMPUTIN | G CENTER | - CENTRO NACIONAL DE SUPERCOMPUTACION |

| Short name: BS                              | C                     |             |          |                                       |

| Address of the orga                         | anisation             |             |          |                                       |

| Street                                      | Calle Jordi Girona 31 |             |          |                                       |

| Town                                        | BARCELONA             |             |          |                                       |

| Postcode                                    | 08034                 |             |          |                                       |

| Country                                     | Spain                 |             |          |                                       |

| Webpage                                     | www.bsc.es            |             |          |                                       |

#### **Research and Innovation legal statuses**

| Public bodyyes                                    |

|---------------------------------------------------|

| Non-profityes                                     |

| International organisationno                      |

| International organisation of European interestno |

| Secondary or Higher education establishmentno     |

| Research organisationyes                          |

#### **Enterprise Data**

| SME self-declared status | 01/03/2005 - no |

|--------------------------|-----------------|

| SME self-assessment      | unknown         |

| SME validation sme       | unknown         |

Based on the above details of the Beneficiary Registry the organisation is not an SME (small- and medium-sized enterprise) for the call.

H2020-CP-2016-v2.pdf Ver1.00 20170223

Page 9 of 30

Legal person ..... yes

#### Dependencies with other proposal participants

| Character of dependence | Participant |  |

|-------------------------|-------------|--|

|-------------------------|-------------|--|

This proposal version was submitted by Angelos BILAS on 26/09/2017 07:43:10 Brussels Local Time. Issued by the Participant Portal Submission Service.

| European Commission<br>Research & Innovation - Participant Portal<br>Proposal Submission Forms |                                                                        |         |            |              |                          |                                                          |

|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|---------|------------|--------------|--------------------------|----------------------------------------------------------|

| Prop                                                                                           | oosal ID 800929                                                        | Acronym | DIO        | Short name   | BSC                      |                                                          |

| Person in cha                                                                                  | rge of the proposal                                                    |         |            |              |                          |                                                          |

|                                                                                                | ail of contact persons are read-o<br>ntact details of contact persons, |         |            |              |                          | an be edited here. To give access<br>I save the changes. |

| Title                                                                                          | Prof.                                                                  |         |            | Sex          | <ul> <li>Male</li> </ul> | ○ Female                                                 |

| First name                                                                                     | Toni                                                                   |         |            | Last name    | Cortes                   |                                                          |

| E-Mail                                                                                         | toni.cortes@bsc.es                                                     |         |            |              |                          |                                                          |

| Position in org.                                                                               | Group Leader                                                           |         |            |              |                          | ]                                                        |

| Department                                                                                     | Computer Science                                                       |         |            |              |                          | Same as organisation                                     |

|                                                                                                | Same as organisation ad                                                | ldress  |            |              |                          |                                                          |

| Street                                                                                         | Calle Jordi Girona 31                                                  |         |            |              |                          | ]                                                        |

| Town                                                                                           | BARCELONA                                                              |         |            | Post code 08 | 3034                     |                                                          |

| Country                                                                                        | Spain                                                                  |         |            |              |                          |                                                          |

| Website                                                                                        | www.bsc.es                                                             |         |            |              |                          |                                                          |

| Phone 1                                                                                        | +34 934137966                                                          | Phone 2 | +34 934137 | 569          | Fax                      | +XXX XXXXXXXXX                                           |

| Other contact                                                                                  | persons                                                                |         |            |              |                          |                                                          |

| First Name | Last Name | E-mail                 | Phone         |

|------------|-----------|------------------------|---------------|

| Ramón      | Nou       | ramon.nou@bsc.es       | +34 934137569 |

| Isabel     | Martinez  | isabel.martinez@bsc.es | +34 934137075 |

| Alberto    | Miranda   | alberto.miranda@bsc.es |               |

H2020-CP-2016-v2.pdf Ver1.00 20170223

Page 11 of 30

European Commission Research & Innovation - Participant Portal

| European<br>European<br>European       |                                                         |  |  |  |  |  |

|----------------------------------------|---------------------------------------------------------|--|--|--|--|--|

| Propos                                 | esal ID 800929 Acronym DIO Short name STFC              |  |  |  |  |  |

| <b>PIC</b><br>999980179                | Legal name<br>SCIENCE AND TECHNOLOGY FACILITIES COUNCIL |  |  |  |  |  |

| Short name: ST                         | FC                                                      |  |  |  |  |  |

| Address of the orga                    | anisation                                               |  |  |  |  |  |

| Street Polaris House North Star Avenue |                                                         |  |  |  |  |  |

| Town                                   | SWINDON                                                 |  |  |  |  |  |

| Postcode                               | SN2 1SZ                                                 |  |  |  |  |  |

| Country                                | United Kingdom                                          |  |  |  |  |  |

| Webpage                                | www.scitech.ac.uk                                       |  |  |  |  |  |

| Legal Status of                        | Legal Status of your organisation                       |  |  |  |  |  |

#### **Research and Innovation legal statuses**

| Public body                                     | .yes      |

|-------------------------------------------------|-----------|

| Non-profit                                      | yes       |

| International organisation                      | . unknown |

| International organisation of European interest | . unknown |

| Secondary or Higher education establishment     | . unknown |

| Research organisation                           | yes       |

#### **Enterprise Data**

| SME self-declared status | 01/04/2007 - no |

|--------------------------|-----------------|

| SME self-assessment      | unknown         |

| SME validation sme       | unknown         |

Based on the above details of the Beneficiary Registry the organisation is not an SME (small- and medium-sized enterprise) for the call.

H2020-CP-2016-v2.pdf Ver1.00 20170223

Page 12 of 30

Legal person ..... yes

#### Dependencies with other proposal participants

| Character of dependence | Participant |  |

|-------------------------|-------------|--|

| Character of dependence | Participant |  |

Page 13 of 30

This proposal version was submitted by Angelos BILAS on 26/09/2017 07:43:10 Brussels Local Time. Issued by the Participant Portal Submission Service.

| EL               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | nnovation - Part<br>Submissior |            |             |         |                                                          |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|------------|-------------|---------|----------------------------------------------------------|

| Prop             | oosal ID 800929                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Acronym                        | DIO        | Short name  | STFC    |                                                          |

| Person in chai   | rge of the proposal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                |            |             |         |                                                          |

|                  | ail of contact persons are rean text details of contact personnact details of contact personnact personna<br>personnact personnact pers |                                |            |             |         | an be edited here. To give access<br>I save the changes. |

| Title            | Dr.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                |            | Sex         | • Male  | ○ Female                                                 |

| First name       | Milos                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                |            | Last name   | Puzovic |                                                          |

| E-Mail           | milos.puzovic@stfc.ac                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | .uk                            |            |             |         |                                                          |

| Position in org. | Research Scientist                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                |            |             |         |                                                          |

| Department       | Future Technologies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                |            |             |         | Same as organisation                                     |

|                  | Same as organisation address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                |            |             |         |                                                          |

| Street           | Sci-Tech Daresbury                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                |            |             |         | ]                                                        |

| Town             | Warrington                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                |            | Post code W | 'A4 4AD |                                                          |

| Country          | United Kingdom                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                |            |             |         |                                                          |

| Website          | http://www.stfc.ac.uk/har                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | tree                           |            |             |         |                                                          |

| F                | -44 1925 603 396                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | а<br>1 Г                       | -XXX XXXXX | XXXX        | Fax     | +XXX XXXXXXXX                                            |

| Other contact    | persons                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                |            |             |         |                                                          |

| First Name       | Last Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | E-mail                         |            |             |         | Phone                                                    |

| First Name | Last Name | E-mail                      | Phone |

|------------|-----------|-----------------------------|-------|

| Michael    | Bane      | michael.bane@stfc.ac.uk     |       |

| Charles    | Moulinec  | charles.moulinec@stfc.ac.uk |       |

Page 14 of 30

| Proposal  | ID 800929  | Acronym | DIO | Short name BULL |

|-----------|------------|---------|-----|-----------------|

| PIC       | Legal name |         |     |                 |

| 996058081 | BULL SAS   |         |     |                 |

|           |            |         |     |                 |

Short name: BULL

Address of the organisation

Street RUE JEAN JAURES 68

Town LES CLAYES SOUS BOIS

- Postcode 78340

- Country France

- Webpage www.bull.com

Legal Status of your organisation

#### **Research and Innovation legal statuses**

| Public bodyno                                     |

|---------------------------------------------------|

| Non-profitno                                      |

| International organisationno                      |

| International organisation of European interestno |

| Secondary or Higher education establishmentno     |

| Research organisationno                           |

#### **Enterprise Data**

| SME self-declared status | unknown |

|--------------------------|---------|

| SME self-assessment      | unknown |

| SME validation sme       | unknown |

Based on the above details of the Beneficiary Registry the organisation is not an SME (small- and medium-sized enterprise) for the call.

Legal person ..... yes

H2020-CP-2016-v2.pdf Ver1.00 20170223

Page 15 of 30

This proposal version was submitted by Angelos BILAS on 26/09/2017 07:43:10 Brussels Local Time. Issued by the Participant Portal Submission Service.

# Country France

#### Dependencies with other proposal participants

| pendence Participant | Character of dependence |

|----------------------|-------------------------|

|----------------------|-------------------------|

Page 16 of 30

This proposal version was submitted by Angelos BILAS on 26/09/2017 07:43:10 Brussels Local Time. Issued by the Participant Portal Submission Service.

|                  | Research &                                                 | Commission<br>& Innovation - Par<br>al Submissioi |           |              |                          |                                                          |

|------------------|------------------------------------------------------------|---------------------------------------------------|-----------|--------------|--------------------------|----------------------------------------------------------|

|                  | Inopean<br>Inomission                                      |                                                   |           |              |                          |                                                          |

| Prop             | oosal ID 800929                                            | Acronym                                           | DIO       | Short name   | BULL                     |                                                          |

| Person in chai   | rge of the proposal                                        |                                                   |           |              |                          |                                                          |

|                  | ail of contact persons are<br>ntact details of contact per |                                                   |           |              |                          | an be edited here. To give access<br>I save the changes. |

| Title            | Dr.                                                        |                                                   |           | Sex          | <ul> <li>Male</li> </ul> | ○ Female                                                 |

| First name       | Huy Nam                                                    |                                                   |           | Last name    | Nguyen                   |                                                          |

| E-Mail           | huy-nam.nguyen@bi                                          | ull.net                                           |           |              |                          |                                                          |

| Position in org. | Head of MVS                                                |                                                   |           |              |                          | ]                                                        |

| Department       | HPC and Server Desig                                       | gn Department                                     |           |              |                          | Same as organisation                                     |

|                  | Same as organisat                                          | ion address                                       |           |              |                          |                                                          |

| Street           | RUE JEAN JAURES 6                                          | 8                                                 |           |              |                          | ]                                                        |

| Town             | LES CLAYES SOUS E                                          | BOIS                                              |           | Post code 78 | 3340                     | ]                                                        |

| Country          | France                                                     |                                                   |           |              |                          | ]                                                        |

| Website          | www.bull.com                                               |                                                   |           |              |                          | ]                                                        |

| Phone 1 +        | -33130806019                                               | Phone 2                                           | +XXX XXXX | 000000       | Fax                      | +33130806157                                             |

| Порс                    | osal ID 800929                    | Acronym      | DIO       | Short name JGU MAINZ |

|-------------------------|-----------------------------------|--------------|-----------|----------------------|

| <b>PIC</b><br>999978627 | <b>Legal name</b><br>JOHANNES GUT | ENBERG-UNIVE | ERSITAT N | IAINZ                |

| Short name: JO          | GU MAINZ                          |              |           |                      |

| Address of the org      | anisation                         |              |           |                      |

| Stree                   | t SAARSTRASSE 21                  |              |           |                      |

| Towr                    | MAINZ                             |              |           |                      |

| Postcode                | e 55099                           |              |           |                      |

| Country                 | Germany                           |              |           |                      |

|                         |                                   |              |           |                      |

#### **Research and Innovation legal statuses**

| Public bodyyes                                    |

|---------------------------------------------------|

| Non-profityes                                     |

| International organisationno                      |

| International organisation of European interestno |

| Secondary or Higher education establishment yes   |

| Research organisationyes                          |

#### **Enterprise Data**

| SME self-declared status | 17/07/2014 - no |

|--------------------------|-----------------|

| SME self-assessment      | unknown         |

| SME validation sme       | unknown         |

Based on the above details of the Beneficiary Registry the organisation is not an SME (small- and medium-sized enterprise) for the call.

H2020-CP-2016-v2.pdf Ver1.00 20170223

Page 18 of 30

Legal person ..... yes

#### Dependencies with other proposal participants

| Character of dependence Participant |

|-------------------------------------|

|-------------------------------------|

H2020-CP-2016-v2.pdf Ver1.00 20170223

Page 19 of 30

This proposal version was submitted by Angelos BILAS on 26/09/2017 07:43:10 Brussels Local Time. Issued by the Participant Portal Submission Service.

|                  | Joppean<br>Joppean<br>Jommission | European Commis<br>Research & Innov<br>Proposal Sub      | ation - Par | •          |               |                          |                                                    |

|------------------|----------------------------------|----------------------------------------------------------|-------------|------------|---------------|--------------------------|----------------------------------------------------|