# Horizon 2020

# **Call: H2020-FETHPC-2016-2017** (FET Proactive – High Performance Computing)

# Topic: FETHPC-01-2016

# **Type of action: RIA** (Research and Innovation action)

# Proposal number: 754313

# **Proposal acronym: ITHACA**

# Deadline Id: H2020-FETHPC-2016 Table of contents

| Section | Title                   | Action |

|---------|-------------------------|--------|

| 1       | General information     |        |

| 2       | Participants & contacts |        |

| 3       | Budget                  |        |

| 4       | Ethics                  |        |

| 5       | Call-specific questions |        |

## How to fill in the forms

The administrative forms must be filled in for each proposal using the templates available in the submission system. Some data fields in the administrative forms are pre-filled based on the previous steps in the submission wizard.

Page 1 of 49

Data Management, Interconnect

| Proposal ID 754313 | Acronym ITHACA                                                                                                                |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------|

| 1 - General i      | nformation                                                                                                                    |

| Торіс              | FETHPC-01-2016                                                                                                                |

| Call Identifier    | H2020-FETHPC-2016-2017                                                                                                        |

| Type of Action     | RIA                                                                                                                           |

| Deadline Id        | H2020-FETHPC-2016                                                                                                             |

| Acronym IT         | HACA                                                                                                                          |

| Proposal title*    | Innovative Technologies for HPC Applications and Computer Architectures                                                       |

|                    | Note that for technical reasons, the following characters are not accepted in the Proposal Title and will be removed: < > " & |

| Duration in months | 36                                                                                                                            |

| Fixed keyword 1    | Computer systems, parallel/distributed systems, grid, cloud proc Add                                                          |

| Fixed keyword 2    | Software Design & Development Add Remove                                                                                      |

| Fixed keyword 3    | High performance computing     Add     Remove                                                                                 |

Free keywords

Page 2 of 49

Proposal ID 754313

Acronym ITHACA

### Abstract

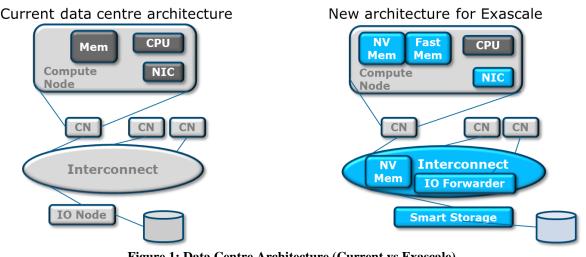

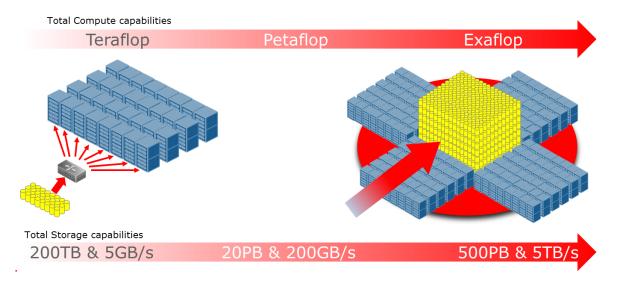

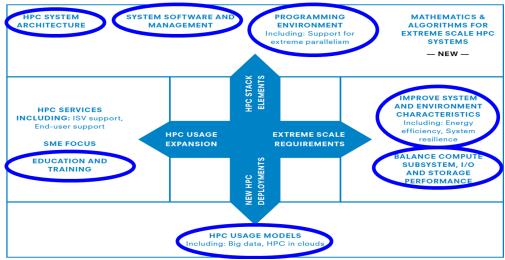

The advent of Exascale HPC systems will enable significant advances in fundamental scientific fields (such as high energy physics, chemistry and material science...), important industrial sectors (including automotive, aeronautics, energy and complex system optimisation...) and complex societal challenges (in the areas of climatology, medicine, energy, large cities management...). However, building HPC systems for Extreme Scale Computing (ESC) poses a number of technological challenges. Exascale is characterized not just by the availability of exaflop computational capability, but also by the massive volumes of data required by simulations running on such systems.

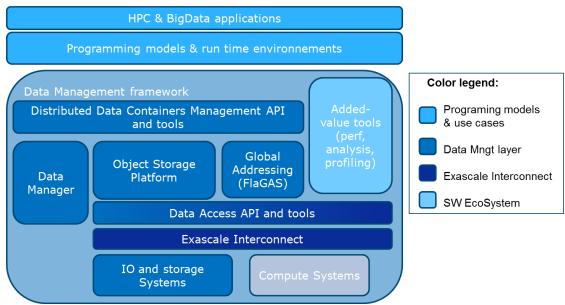

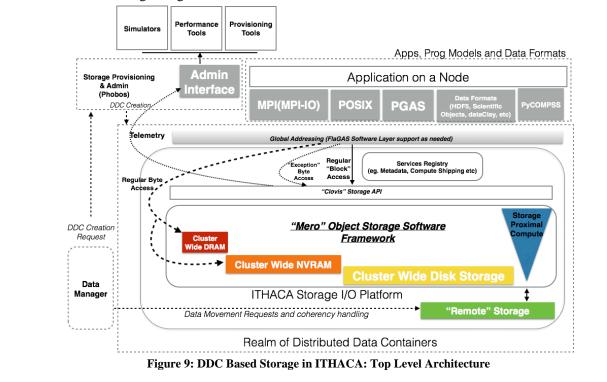

ITHACA will benefit from the results of the ongoing H2020 SAGE project to innovate a new IO object storage framework, and also from the Bull eXascale Interconnect (BXI) technology. ITHACA will complement the H2020 Mont-Blanc 3 project which is focussed on providing a new efficient CPU for HPC systems.

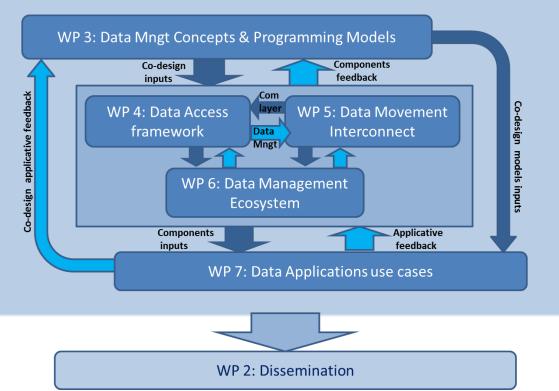

Therefore, the ITHACA project will incorporate research findings innovation in hardware technologies and newly enabled software, with the objective of designing and developing a set of new components required for the efficient and scalable data management framework. Amongst the set of principal components, this project will implement an enriched generation of the interconnect, will update and evaluate the best programming models for such an architecture, and will develop advanced data containers objects, an efficient data manager service, a new global addressing mechanism, added-values tools and libraries, and will use these components via a set of key scientific and big data applications.

Thus, the ITHACA project aims to provide data management component developments, design specifications and associated simulation tools needed to deliver an Exascale compute-capable data management solution for horizon 2020.

Remaining characters 107

Has this proposal (or a very similar one) been submitted in the past 2 years in response to a call for proposals under the 7th Framework Programme, Horizon 2020 or any other EU programme(s)?

Proposal ID 754313

Acronym ITHACA

## Declarations

| 1) The coordinator declares to have the explicit consent of all applicants on their participation and on the content of this proposal.                                                                                                                                                                     | $\boxtimes$ |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 2) The information contained in this proposal is correct and complete.                                                                                                                                                                                                                                     | $\boxtimes$ |

| 3) This proposal complies with ethical principles (including the highest standards of research integrity — as set out, for instance, in the European Code of Conduct for Research Integrity — and including, in particular, avoiding fabrication, falsification, plagiarism or other research misconduct). | $\boxtimes$ |

#### 4) The coordinator confirms:

|   | - to have carried out the self-check of the financial capacity of the organisation on <a href="http://ec.europa.eu/research/participants/portal/desktop/en/organisations/lfv.html">http://ec.europa.eu/research/participants/portal/desktop/en/organisations/lfv.html</a> or to be covered by a financial viability check in an EU project for the last closed financial year. Where the result was "weak" or "insufficient", the coordinator confirms being aware of the measures that may be imposed in accordance with the H2020 Grants Manual (Chapter on Financial capacity check); or | ۲ |  |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--|

|   | - is exempt from the financial capacity check being a public body including international organisations, higher or secondary education establishment or a legal entity, whose viability is guaranteed by a Member State or associated country, as defined in the H2020 Grants Manual (Chapter on Financial capacity check); or                                                                                                                                                                                                                                                              | О |  |

| Ī | - as sole participant in the proposal is exempt from the financial capacity check.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | О |  |

5) The coordinator hereby declares that each applicant has confirmed:

| - they are fully eligible in accordance with the criteria set out in the specific call for proposals; and          | $\boxtimes$  |

|--------------------------------------------------------------------------------------------------------------------|--------------|

| - they have the financial and operational capacity to carry out the proposed action.                               | $\boxtimes$  |

| The coordinator is only responsible for the correctness of the information relating to his/ber own organisation Ea | ch applicant |

The coordinator is only responsible for the correctness of the information relating to his/her own organisation. Each applicant remains responsible for the correctness of the information related to him/her and declared above. Where the proposal to be retained for EU funding, the coordinator and each beneficiary applicant will be required to present a formal declaration in this respect.

According to Article 131 of the Financial Regulation of 25 October 2012 on the financial rules applicable to the general budget of the Union (Official Journal L 298 of 26.10.2012, p. 1) and Article 145 of its Rules of Application (Official Journal L 362, 31.12.2012, p.1) applicants found guilty of misrepresentation may be subject to administrative and financial penalties under certain conditions.

#### Personal data protection

The assessment of your grant application will involve the collection and processing of personal data (such as your name, address and CV), which will be performed pursuant to Regulation (EC) No 45/2001 on the protection of individuals with regard to the processing of personal data by the Community institutions and bodies and on the free movement of such data. Unless indicated otherwise, your replies to the questions in this form and any personal data requested are required to assess your grant application in accordance with the specifications of the call for proposals and will be processed solely for that purpose. Details concerning the purposes and means of the processing of your personal data as well as information on how to exercise your rights are available in the <u>privacy statement</u>. Applicants may lodge a complaint about the processing of their personal data with the European Data Protection Supervisor at any time.

Your personal data may be registered in the Early Detection and Exclusion system of the European Commission (EDES), the new system established by the Commission to reinforce the protection of the Union's financial interests and to ensure sound financial management, in accordance with the provisions of articles 105a and 108 of the revised EU Financial Regulation (FR) (Regulation (EU, EURATOM) 2015/1929 of the European Parliament and of the Council of 28 October 2015 amending Regulation (EU, EURATOM) No 966/2012) and articles 143 - 144 of the corresponding Rules of Application (RAP) (COMMISSION DELEGATED REGULATION (EU) 2015/2462 of 30 October 2015 amending Delegated Regulation (EU) No 1268/2012) for more information see the Privacy statement for the EDES Database).

Page 4 of 49

Proposal ID 754313

Acronym ITHACA

# List of participants

| #  | Participant Legal Name                                                | Country        |

|----|-----------------------------------------------------------------------|----------------|

| 1  | BULL SAS                                                              | France         |

| 2  | SEAGATE SYSTEMS UK LIMITED                                            | United Kingdom |

| 3  | COMMISSARIAT A L ENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES        | France         |

| 4  | UNIVERSITAT POLITECNICA DE VALENCIA                                   | Spain          |

| 5  | UNIVERSIDAD DE CASTILLA - LA MANCHA                                   | Spain          |

| 6  | DEUTSCHES KLIMARECHENZENTRUM GMBH                                     | Germany        |

| 7  | FRAUNHOFER GESELLSCHAFT ZUR FOERDERUNG DER ANGEWANDTEN FORSCHUNG E.V. | Germany        |

| 8  | BARCELONA SUPERCOMPUTING CENTER - CENTRO NACIONAL DE SUPERCOMPUTACION | Spain          |

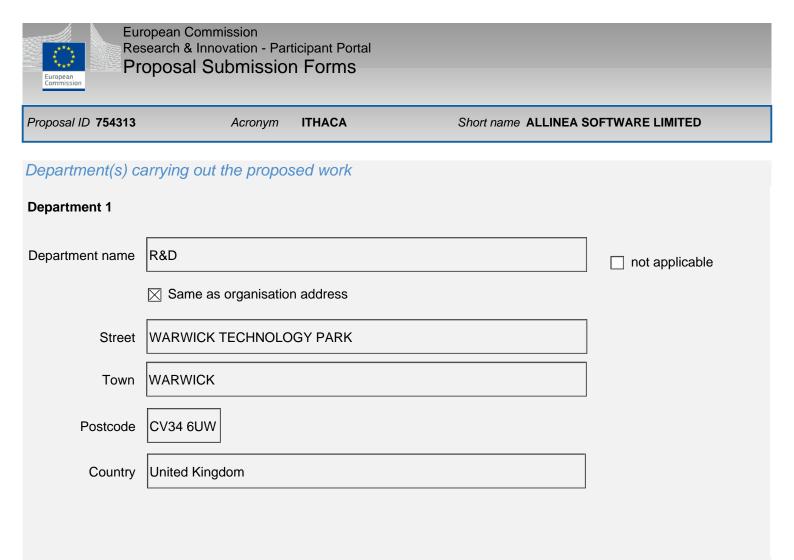

| 9  | ALLINEA SOFTWARE LIMITED                                              | United Kingdom |

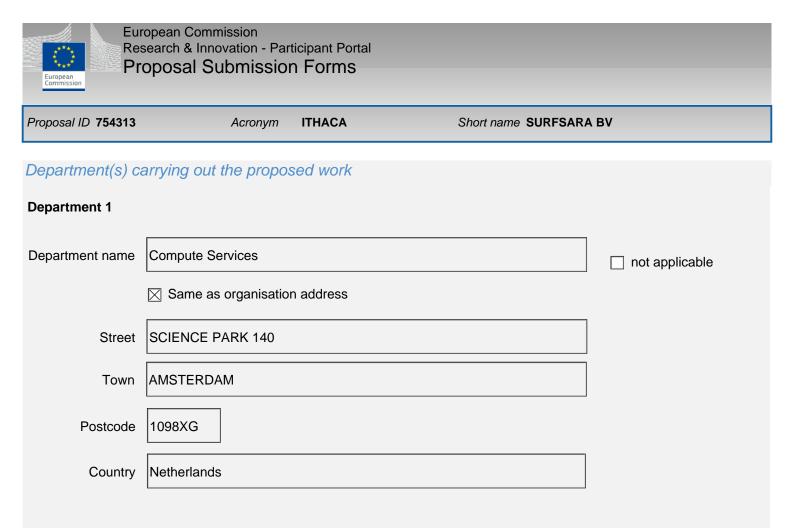

| 10 | SURFSARA BV                                                           | Netherlands    |

| 11 | INSTITUT NATIONAL DE RECHERCHE ENINFORMATIQUE ET AUTOMATIQUE          | France         |

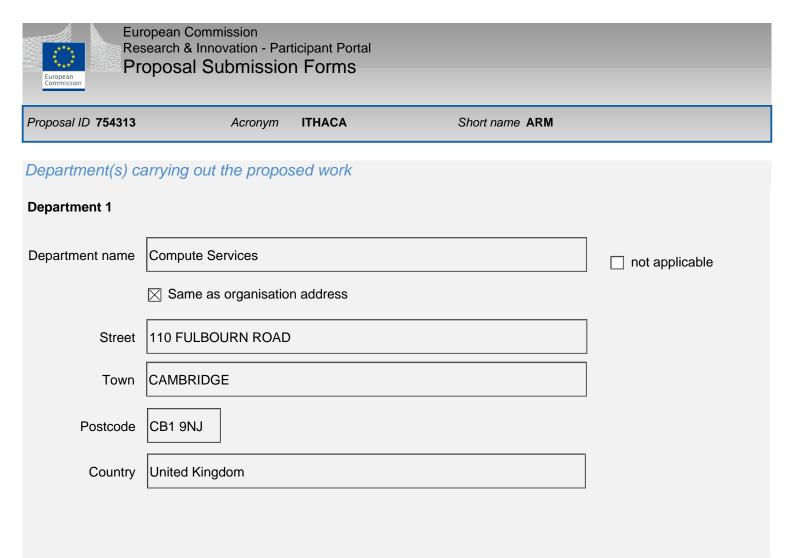

| 12 | ARM LIMITED                                                           | United Kingdom |

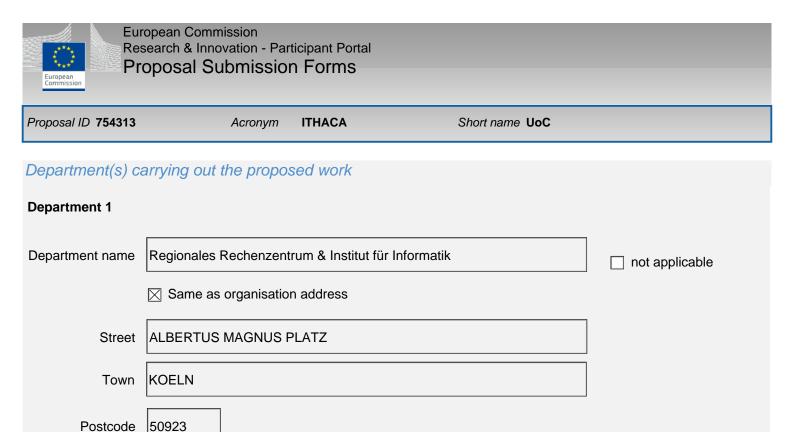

| 13 | UNIVERSITAET ZU KOELN                                                 | Germany        |

This proposal version was submitted by bruno FARCY on 27/09/2016 16:27:49 Brussels Local Time. Issued by the Participant Portal Submission Service.

Proposal ID 754313

Acronym

ITHACA

Short name

BULL

2 - Administrative data of participating organisations

PIC

Legal name

996058081

BULL SAS

Short name: BULL

Address of the organisation

Street

RUE JEAN JAURES 68

Town

LES CLAYES SOUS BOIS

Postcode 78340

Country France

Webpage www.bull.com

Legal Status of your organisation

### **Research and Innovation legal statuses**

| Public bodyno                                     | Legal person yes |

|---------------------------------------------------|------------------|

| Non-profitno                                      |                  |

| International organisationno                      |                  |

| International organisation of European interestno |                  |

| Secondary or Higher education establishment no    |                  |

| Research organisationno                           |                  |

| Enterprise Data                                   |                  |

| SME self-declared status | unknown |

|--------------------------|---------|

| SME self-assessment      | unknown |

| SME validation sme       | unknown |

Based on the above details of the Beneficiary Registry the organisation is not an SME (small- and medium-sized enterprise) for the call.

NACE Code: 6202 - Computer consultancy and computer facilities management activities

H2020-CP-2016.pdf Ver1.00 20160617

Page 6 of 49

| Character of dependence | Participant |  |  |

|-------------------------|-------------|--|--|

|-------------------------|-------------|--|--|

| i 🖓 🔨 🔤                               | European Comm<br>Research & Inno<br>Proposal Su | vation - Part | •       |            |              |                          |                                                     |

|---------------------------------------|-------------------------------------------------|---------------|---------|------------|--------------|--------------------------|-----------------------------------------------------|

| Proposal ID 75431                     | 13                                              | Acronym       | ITHACA  |            | Short name   | BULL                     |                                                     |

| Person in chai                        | rge of the prop                                 | oosal         |         |            |              |                          |                                                     |

| The name and e-m rights and basic con |                                                 |               |         |            |              |                          | an be edited here. To give access save the changes. |

| Title                                 | Mr.                                             |               |         |            | Sex          | <ul> <li>Male</li> </ul> | ○ Female                                            |

| First name                            | bruno                                           |               |         |            | Last name    | FARCY                    |                                                     |

| E-Mail                                | bruno.farcy@b                                   | oull.net      |         |            |              |                          |                                                     |

| Position in org.                      | R&D Program                                     | Manager       |         |            |              |                          |                                                     |

| Department                            | R&D                                             |               |         |            |              |                          | Same as organisation                                |

|                                       | 🔀 Same as org                                   | ganisation ad | ddress  |            |              |                          |                                                     |

| Street                                | RUE JEAN JAL                                    | JRES 68       |         |            |              |                          | ]                                                   |

| Town                                  | LES CLAYES S                                    | OUS BOIS      |         |            | Post code 78 | 8340                     |                                                     |

| Country                               | France                                          |               |         |            |              |                          |                                                     |

| Website                               | www.bull.com                                    |               |         |            |              |                          |                                                     |

| Phone 1 +                             | -33 130807620                                   |               | Phone 2 | +XXX XXXXX | XXXX         | Fax                      | +XXX XXXXXXXXX                                      |

## Other contact persons

| First Name | Last Name | E-mail                   | Phone        |

|------------|-----------|--------------------------|--------------|

| Medur      | Sridharan | medur.sridharan@bull.net | +33130803024 |

Page 8 of 49

| Proposal ID 754313      | Acronym                              | ITHACA       | Short name SEAGATE SYSTEMS |

|-------------------------|--------------------------------------|--------------|----------------------------|

|                         | <b>Legal name</b><br>SEAGATE SYSTEMS | S UK LIMITED |                            |

| Short name: SEAG        | ATE SYSTEMS                          |              |                            |

| Address of the organisa | ation                                |              |                            |

| Street LA               | NGSTONE ROAD                         |              |                            |

| Town HA                 | VANT                                 |              |                            |

| Postcode PC             | 9 1SA                                |              |                            |

| Country Un              | ited Kingdom                         |              |                            |

| Webpage                 |                                      |              |                            |

| Legal Status of you     | r organisation                       |              |                            |

Legal person ..... yes

### **Research and Innovation legal statuses**

| Public bodyno                                      |

|----------------------------------------------------|

| Non-profitno                                       |

| International organisationno                       |

| International organisation of European interest no |

| Secondary or Higher education establishment no     |

| Research organisationno                            |

|                                                    |

## **Enterprise Data**

| SME self-declared status | unknown |

|--------------------------|---------|

| SME self-assessment      | unknown |

| SME validation sme       | unknown |

Based on the above details of the Beneficiary Registry the organisation is not an SME (small- and medium-sized enterprise) for the call.

NACE Code: 2620 - Manufacture of computers and peripheral equipment

H2020-CP-2016.pdf Ver1.00 20160617

Page 9 of 49

| Character of dependence | Participant |  |  |

|-------------------------|-------------|--|--|

|-------------------------|-------------|--|--|

| F The second sec | European Commiss<br>Research & Innovat<br>Proposal Subr | ion - Part  |           |           | -           | ٠                        |                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-------------|-----------|-----------|-------------|--------------------------|----------------------------------------------------------|

| Proposal ID 75431                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1 <b>3</b> A                                            | cronym      | ITHACA    |           | Short name  | SEAGATE                  | SYSTEMS                                                  |

| Person in char                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | rge of the propos                                       | sal         |           |           |             |                          |                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ail of contact persons<br>ntact details of contac       |             |           |           |             |                          | an be edited here. To give access<br>I save the changes. |

| Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Mr.                                                     |             |           |           | Sex         | <ul> <li>Male</li> </ul> | ○ Female                                                 |

| First name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Sai                                                     |             |           |           | Last name   | Narasimh                 | namurthy                                                 |

| E-Mail                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | sai.narasimhamu                                         | rthy@sea    | agate.com | ı         |             |                          |                                                          |

| Position in org.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Staff Engineer                                          |             |           |           |             |                          | ]                                                        |

| Department                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Seagate Systems                                         | Group       |           |           |             |                          | Same as organisation                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 🔀 Same as orgar                                         | nisation ac | ddress    |           |             |                          |                                                          |

| Street                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | LANGSTONE RO                                            | AD          |           |           |             |                          | ]                                                        |

| Town                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | HAVANT                                                  |             |           |           | Post code P | O9 1SA                   |                                                          |

| Country                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | United Kingdom                                          |             |           |           |             |                          |                                                          |

| Website                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                         |             |           |           |             |                          |                                                          |

| Phone 1 +                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 44 2392496648                                           |             | Phone 2   | +44 75840 | 80691       | Fax                      | +XXX XXXXXXXXX                                           |

Page 11 of 49

| Proposal ID 754313      | Acronym                               | ITHACA     | Short name CEA                      |

|-------------------------|---------------------------------------|------------|-------------------------------------|

| <b>PIC</b><br>999992401 | <b>Legal name</b><br>COMMISSARIAT A L | ENERGIE AT | OMIQUE ET AUX ENERGIES ALTERNATIVES |

| Short name: CEA         |                                       |            |                                     |

| Address of the organis  | sation                                |            |                                     |

| Street R                | UE LEBLANC 25                         |            |                                     |

| Town P                  | ARIS 15                               |            |                                     |

| Postcode 7              | 5015                                  |            |                                     |

| Country F               | rance                                 |            |                                     |

| Webpage w               | ww.cea.fr                             |            |                                     |

| Legal Status of yo      | ur organisation                       |            |                                     |

|                         |                                       |            |                                     |

Legal person ..... yes

#### **Research and Innovation legal statuses**

| Public bodyyes                                     |

|----------------------------------------------------|

| Non-profityes                                      |

| International organisationno                       |

| International organisation of European interest no |

| Secondary or Higher education establishment no     |

| Research organisationyes                           |

|                                                    |

## **Enterprise Data**

| SME self-declared status | 2007 - no |

|--------------------------|-----------|

| SME self-assessment      | unknown   |

| SME validation sme       | 2007 - no |

Based on the above details of the Beneficiary Registry the organisation is not an SME (small- and medium-sized enterprise) for the call.

NACE Code: - - Not applicable

H2020-CP-2016.pdf Ver1.00 20160617

Page 12 of 49

| Character of dependence | Participant |  |  |

|-------------------------|-------------|--|--|

|-------------------------|-------------|--|--|

| - <b></b>         | European Commissio<br>Research & Innovatio<br>Proposal Subm | on - Partic | •       | al         |                          |                          |                                                          |

|-------------------|-------------------------------------------------------------|-------------|---------|------------|--------------------------|--------------------------|----------------------------------------------------------|

| Proposal ID 75431 | 1 <b>3</b> Ac                                               | ronym       | ITHACA  |            | Short name               | CEA                      |                                                          |

| Person in chai    | rge of the propos                                           | al          |         |            |                          |                          |                                                          |

|                   | ail of contact persons a<br>ntact details of contact        |             |         |            |                          |                          | an be edited here. To give access<br>I save the changes. |

| Title             | Mr.                                                         |             |         |            | Sex                      | <ul> <li>Male</li> </ul> | ○ Female                                                 |

| First name        | Jacques-Charles                                             |             |         |            | Last name                | Lafoucrie                | ère                                                      |

| E-Mail            | jacques-charles.la                                          | foucriere   | @cea.fr |            |                          |                          |                                                          |

| Position in org.  | Head of Service                                             |             |         |            |                          |                          | ]                                                        |

| Department        | DAM                                                         |             |         |            |                          |                          | Same as organisation                                     |

|                   | Same as organis                                             | sation add  | dress   |            |                          |                          |                                                          |

| Street            | CEA/DIF - Bruyères                                          | s le Châte  |         |            |                          |                          | ]                                                        |

| Town              | ARPAJON                                                     |             |         |            | Post code 9 <sup>-</sup> | 1297                     | ]                                                        |

| Country           | France                                                      |             |         |            |                          |                          |                                                          |

| Website           |                                                             |             |         |            |                          |                          | ]                                                        |

| Phone 1 +         | -33 169266727                                               |             | Phone 2 | +XXX XXXXX | XXXX                     | Fax                      | +XXX XXXXXXXXX                                           |

Page 14 of 49

| Proposal ID 754313   | Acronym ITHACA                      | Short name UPV |

|----------------------|-------------------------------------|----------------|

| PIC                  | Legal name                          |                |

| 999864846            | UNIVERSITAT POLITECNICA DE VALENCIA |                |

| Short name: UPV      |                                     |                |

| Address of the organ | sation                              |                |

| Street (             | CAMINO DE VERA SN EDIFICIO 3A       |                |

| Town \               | /ALENCIA                            |                |

| Postcode 4           | 6022                                |                |

| Country S            | Spain                               |                |

| Webpage v            | /ww.upv.es                          |                |

| Legal Status of yo   | our organisation                    |                |

|                      |                                     |                |

Legal person ..... yes

#### **Research and Innovation legal statuses**

| Public bodyyes                                     |

|----------------------------------------------------|

| Non-profityes                                      |

| International organisationno                       |

| International organisation of European interest no |

| Secondary or Higher education establishment yes    |

| Research organisationyes                           |

|                                                    |

## **Enterprise Data**

| SME self-declared status | .2012 - no |

|--------------------------|------------|

| SME self-assessment      | unknown    |

| SME validation sme       | unknown    |

Based on the above details of the Beneficiary Registry the organisation is not an SME (small- and medium-sized enterprise) for the call.

NACE Code: 853 - Higher education

H2020-CP-2016.pdf Ver1.00 20160617

Page 15 of 49

| Character of dependence | Participant |  |  |

|-------------------------|-------------|--|--|

|-------------------------|-------------|--|--|

Page 16 of 49

| 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | European Comm<br>Research & Inno<br>Proposal Su | vation - Part |          |             |              |        |                                                    |

|---------------------------------------|-------------------------------------------------|---------------|----------|-------------|--------------|--------|----------------------------------------------------|

| European<br>Commission                |                                                 |               |          |             |              |        |                                                    |

| Proposal ID 75431                     | 13                                              | Acronym       | ITHACA   |             | Short name   | UPV    |                                                    |

| Person in chai                        | rge of the prop                                 | oosal         |          |             |              |        |                                                    |

| The name and e-m rights and basic col |                                                 |               |          |             |              |        | n be edited here. To give access save the changes. |

| Title                                 | Prof.                                           |               |          |             | Sex          | • Male | ⊂ Female                                           |

| First name                            | Jose                                            |               |          |             | Last name    | Duato  |                                                    |

| E-Mail                                | jduato@disca.                                   | upv.es        |          |             |              |        |                                                    |

| Position in org.                      | Professor                                       |               |          |             |              |        |                                                    |

| Department                            | DISCA                                           |               |          |             |              |        | Same as organisation                               |

|                                       | 🔀 Same as org                                   | ganisation ac | dress    |             |              |        |                                                    |

| Street                                | CAMINO DE VE                                    | ERA SN EDI    | FICIO 3A |             |              |        | ]                                                  |

| Town                                  | VALENCIA                                        |               |          |             | Post code 46 | 6022   |                                                    |

| Country                               | Spain                                           |               |          |             |              |        |                                                    |

| Website                               |                                                 |               |          |             |              |        |                                                    |

| Phone 1 +                             | -34 963 879705                                  |               | Phone 2  | +XXX XXXXXX | XXX          | Fax    | +XXX XXXXXXXXX                                     |

## Other contact persons

| First Name     | Last Name     | E-mail               | Phone |

|----------------|---------------|----------------------|-------|

| Maria Engracia | Gomez Requena | megomez@disca.upv.es |       |

Page 17 of 49

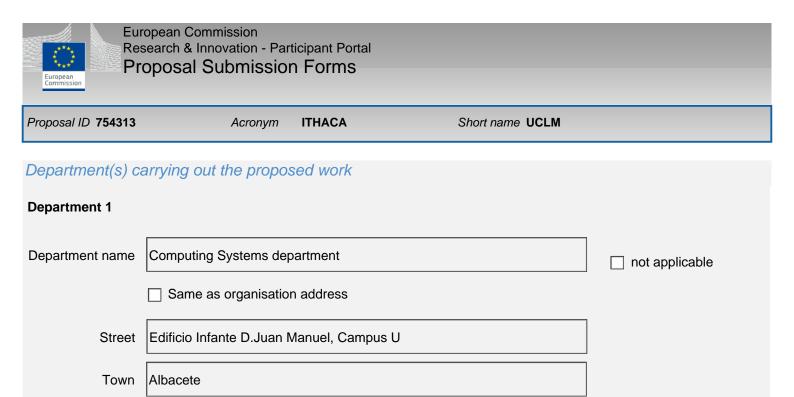

| Proposal ID 754313      | Acronym                                | ITHACA       | Short name UCLM |  |

|-------------------------|----------------------------------------|--------------|-----------------|--|

| <b>PIC</b><br>999840208 | <b>Legal name</b><br>UNIVERSIDAD DE C. | ASTILLA - LA | MANCHA          |  |

| Short name: UCL         | M                                      |              |                 |  |

| Address of the organ    | isation                                |              |                 |  |

| Street (                | CALLE ALTAGRACIA 50                    | )            |                 |  |

| Town (                  | CIUDAD REAL                            |              |                 |  |

| Postcode 1              | 3071                                   |              |                 |  |

| Country S               | Spain                                  |              |                 |  |

| Webpage v               | vww.uclm.es                            |              |                 |  |

| Legal Status of yo      | our organisation                       |              |                 |  |

|                         |                                        |              |                 |  |

Legal person ..... yes

#### **Research and Innovation legal statuses**

| Public bodyyes                                    |

|---------------------------------------------------|

| Non-profityes                                     |

| International organisationno                      |

| International organisation of European interestno |

| Secondary or Higher education establishment yes   |

| Research organisationyes                          |

|                                                   |

## **Enterprise Data**

| SME self-declared status | . 1981 - no |

|--------------------------|-------------|

| SME self-assessment      | unknown     |

| SME validation sme       | unknown     |

Based on the above details of the Beneficiary Registry the organisation is not an SME (small- and medium-sized enterprise) for the call.

NACE Code: 853 - Higher education

H2020-CP-2016.pdf Ver1.00 20160617

Page 18 of 49

02071

Spain

Postcode

Country

| Character of dependence | Participant |  |

|-------------------------|-------------|--|

|-------------------------|-------------|--|

Page 19 of 49

| - <b></b>                               | European Comm<br>Research & Inno<br>Proposal Su | vation - Parti | •         |               |              |                          |                                                        |

|-----------------------------------------|-------------------------------------------------|----------------|-----------|---------------|--------------|--------------------------|--------------------------------------------------------|

| Proposal ID <b>7543</b> 1               | 13                                              | Acronym        | ITHACA    |               | Short name   | UCLM                     |                                                        |

| Person in chai                          | rge of the prop                                 | oosal          |           |               |              |                          |                                                        |

| The name and e-m<br>rights and basic co |                                                 |                |           |               |              |                          | an be edited here. To give access<br>save the changes. |

| Title                                   | Dr.                                             |                |           |               | Sex          | <ul> <li>Male</li> </ul> | ○ Female                                               |

| First name                              | Pedro Javier                                    |                |           |               | Last name    | Garcia G                 | arcia                                                  |

| E-Mail                                  | pedrojavier.ga                                  | rcia@uclm.     | es        |               |              |                          |                                                        |

| Position in org.                        | Assistant profes                                | ssor           |           |               |              |                          |                                                        |

| Department                              | Computing Sys                                   | tems           |           |               |              |                          | Same as organisation                                   |

|                                         | Same as or                                      | ganisation ac  | ldress    |               |              |                          |                                                        |

| Street                                  | Edificio Infante                                | D.Juan Man     | uel, Camp | us Universita | rio, s/n     |                          | ]                                                      |

| Town                                    | Albacete                                        |                |           |               | Post code 02 | 2071                     |                                                        |

| Country                                 | Spain                                           |                |           |               |              |                          |                                                        |

| Website                                 |                                                 |                |           |               |              |                          |                                                        |

| Phone 1 +                               | -34 967599200                                   |                | Phone 2   | +34 657185    | 5891         | Fax                      | +34 967599224                                          |

Page 20 of 49

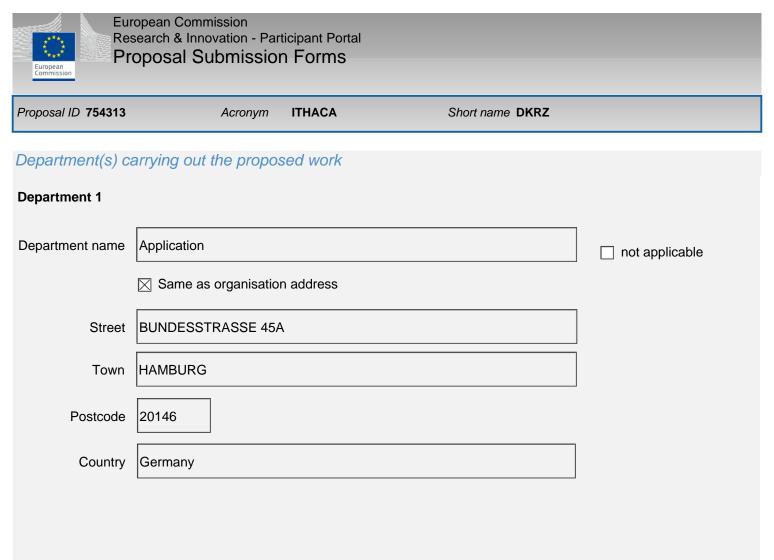

| Proposal ID 754313      | Acronym                       | ITHACA     | Short name DKRZ |  |

|-------------------------|-------------------------------|------------|-----------------|--|

| <b>PIC</b><br>998692310 | Legal name<br>DEUTSCHES KLIMA | RECHENZENT | TRUM GMBH       |  |

| Short name: DKR         | Z                             |            |                 |  |

| Address of the organ    | isation                       |            |                 |  |

| Street E                | BUNDESSTRASSE 45A             |            |                 |  |

| Town H                  | IAMBURG                       |            |                 |  |

| Postcode 2              | 20146                         |            |                 |  |

| Country C               | Sermany                       |            |                 |  |

| Webpage h               | ttp:/www.dkrz.de              |            |                 |  |

| Legal Status of yo      | our organisation              |            |                 |  |

|                         |                               |            |                 |  |

Legal person ..... yes

#### **Research and Innovation legal statuses**

| Public bodyyes                                     |

|----------------------------------------------------|

| Non-profityes                                      |

| International organisationno                       |

| International organisation of European interest no |

| Secondary or Higher education establishment no     |

| Research organisationyes                           |

|                                                    |

## **Enterprise Data**

| SME self-declared status | 2007 - no |

|--------------------------|-----------|

| SME self-assessment      | unknown   |

| SME validation sme       | 2007 - no |

Based on the above details of the Beneficiary Registry the organisation is not an SME (small- and medium-sized enterprise) for the call.

NACE Code: 721 - Research and experimental development on natural sciences and engineering

H2020-CP-2016.pdf Ver1.00 20160617

Page 21 of 49

### **Department 2**

| Department name | WR                           | not applicable |

|-----------------|------------------------------|----------------|

|                 | Same as organisation address |                |

| Street          | BUNDESSTRASSE 45A            |                |

| Town            | HAMBURG                      |                |

| Postcode        | 20146                        |                |

| Country         | Germany                      |                |

## Dependencies with other proposal participants

| Character of dependence | Participant |  |

|-------------------------|-------------|--|

|-------------------------|-------------|--|

H2020-CP-2016.pdf Ver1.00 20160617

Page 22 of 49

|                  | European Comm<br>Research & Inno <sup>.</sup><br>Proposal Su | vation - Par |          |             |              |                          |                                                          |

|------------------|--------------------------------------------------------------|--------------|----------|-------------|--------------|--------------------------|----------------------------------------------------------|

| Proposal ID 7543 | 13                                                           | Acronym      | ITHACA   |             | Short name   | DKRZ                     |                                                          |

| Person in cha    | rge of the prop                                              | osal         |          |             |              |                          |                                                          |